# FULL-BRIDGE PWM MOTOR DRIVERS

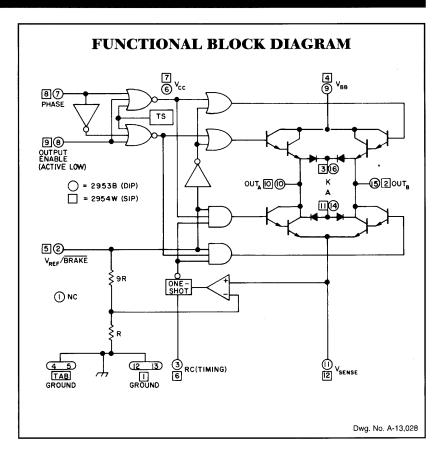

The UDN2953B and UDN2954W are designed for bidirectional control of dc or stepper motors with continuous output currents to 2 A and peak start-up currents as high as 3.5 A. For pulse-width modulated (chopped-mode) operation, the output current is determined by the user's selection of a reference voltage and sensing resister while the OFF pulse duration is set by an external RC timing network PWM operation is characterized by maximum efficience and the power-dissipation levels. Extensive internal circuit practice and cludes the mal shutdown with hysteresis, transient-suppraction liodes, and cross ever current protection.

When the V<sub>REF</sub>/BRAKE pires we cold V), the braking fraction is enabled. This turns both sink triven OFF and the strivers are turned ON. When V<sub>REF</sub>/PC. Kinds at above 2.4 the vortage (and the current sensing resistoned earnines the load current rip point. An RC TIMING pin is available to use for an internal one-shot to control load current decay time.

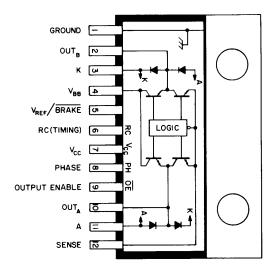

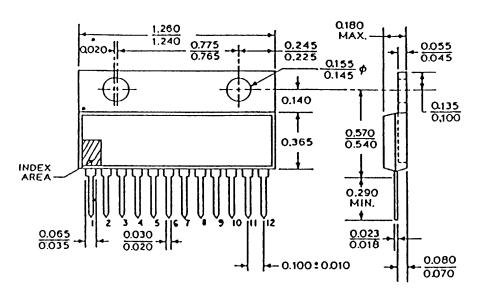

The LOW 953B driver is surgiced like 15-pin dual-in-line plastic package with disper heat-sink contact taos. The lead configuration engages early attachment of a heat-sink while fitting a standard integrate circuit socket or place to tring board layout. The UDN2954W, for higher package rower a scipation requirements, is supplied in a 12- in single in-line rower tao package. In any package style, the lat sink is at a round mential and needs no insulation.

#### FEAT UPE

- 0 X Otra Voltage Rating

- Continuous Output Rating

- Internal Flyback Diodes

- Anermal Shutdown

- Crossover Current Protection

- BRAKE, ENABLE, and Current-Limit Functions

VREF BRAKE 2

RC (TIMING) 3 RC 15 OUTB GROUND GROUND 5 CC 6 SENSE

Dwg. No. A-13,024

OUT

# ABSOLUTE MAXIMULT TINGS

PHASE

OUTPUT ENABLE

| Motor Supply Mage V 5                                  |

|--------------------------------------------------------|

| Output Curre I <sub>OUT</sub>                          |

| (P ar)                                                 |

| Continue s) ±2.J A                                     |

| ba Disae Voltage, V V <sub>ap</sub>                    |

| Mini um Clamp Diod Vol. ge                             |

| V <sub>A</sub> Ground                                  |

| Logic Supply Voltage,                                  |

| Logic Input Voltage,                                   |

| V <sub>PHASE</sub> : ENABLE V <sub>BB</sub>            |

|                                                        |

| - GLNGL                                                |

| Reference Voltage, V <sub>REF</sub> /BRAKE <b>15 V</b> |

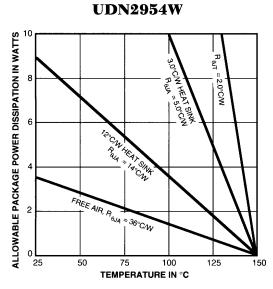

| Package Power Dissipation,                             |

| P <sub>D</sub> See Graphs                              |

| Operating Temperature Range,                           |

| T <sub>A</sub> 20°C to +85°C                           |

| Storage Temperature Range,                             |

| T <sub>S</sub> 55°C to +150°C                          |

|                                                        |

Always order by complete part number:

| Part Number | Package              |  |  |

|-------------|----------------------|--|--|

| UDN2953B    | 16-Pin DIP           |  |  |

| UDN2954W    | 12-Pin Power-Tab SIP |  |  |

# WELLOWABLE PACKAGE POWER DISSIPATION IN WATS AND ADDRESS OF TEMPERATURE IN °C

Dwg. GP-012A

Dwg. GP-010B

#### **TRUTH TABLE**

| Output<br>Enable | Phase | V <sub>REF</sub> /BRAKE | Out <sub>A</sub> | Out <sub>B</sub> |

|------------------|-------|-------------------------|------------------|------------------|

| Low              | High  | > 2.4 V                 | High             | Low              |

| Low              | Low   | > 2.4 V                 | Low              | High             |

| High             | Χ     | > 2.4 V                 | Open             | Open             |

| Х                | Χ     | < 0.8 V                 | High             | High             |

X = Irrelevant

#### **UDN2954W**

Dwg. No. A-13,023

# ELECTRICAL CHARACTERISTICS at T $_A$ = +25°C, T $_J$ $\leq$ +150°C, V $_{BB}$ = 50 V, V $_{CC}$ = 5 V, V $_{SENSE}$ = 0 V, RC = 20 k $\Omega/470$ pF to Ground.

|                                                      |                        |                                                                        | Limits |                    |      |            |

|------------------------------------------------------|------------------------|------------------------------------------------------------------------|--------|--------------------|------|------------|

| Characteristic                                       | Symbol                 | Test Conditions                                                        | Min.   | Тур.               | Max. | Units      |

| Output Drivers (OUT <sub>A</sub> or OUT <sub>B</sub> | )                      |                                                                        |        |                    |      |            |

| Output Supply Range                                  | V <sub>BB</sub>        |                                                                        | 6.5    | _                  | 50   | V          |

| Output Leakage Current                               | I <sub>CEX</sub>       | V <sub>ENABLE</sub> = 5 V, V <sub>OUT</sub> = V <sub>BB</sub> , (note) | _      |                    | 50   | μ <b>A</b> |

|                                                      |                        | V <sub>ENABLE</sub> = 5 V, V <sub>OUT</sub> = 0 V, (note)              | _      | _                  | -50  | μА         |

| Output Sustaining Voltage                            | V <sub>CE(sus)</sub>   | $I_{OUT} = \pm 2 \text{ A, L} = 2 \text{ mH}$                          | 50     | _                  |      | ٧          |

| Output Saturation Voltage                            | V <sub>CE(SAT)</sub>   | $V_{ENABLE} = 0 \text{ V}, I_{OUT} = \pm 0.5 \text{ A}$                | _      | 1.0                | 1.2  | V          |

|                                                      | , ,                    | V <sub>ENABLE</sub> = 0 V, I <sub>OUT</sub> = ±1.0 A                   |        | 1.2                | 1.4  | V          |

|                                                      |                        | $V_{ENABLE} = 0 \text{ V}, I_{OUT} = \pm 2.0 \text{ A}$                |        | 1.5                | 1.8  | V          |

| Clamp Diode Leakage Current                          | I <sub>R</sub>         | V <sub>R</sub> = 50 V                                                  |        |                    | 50   | μА         |

| Clamp Diode Forward Voltage                          | V <sub>F</sub>         | I <sub>F</sub> = 2 A                                                   | _      | 1.8                | 2.2  | ٧          |

| Motor Supply Current                                 | I <sub>BB(ON)</sub>    | V <sub>ENABLE</sub> = 0.8 V, V <sub>REF</sub> = 2.4 V, No Load         | _      | 20                 | 30   | mA         |

|                                                      | I <sub>BB(OFF)</sub>   | V <sub>ENABLE</sub> = V <sub>REF</sub> = 2.4 V, No Load                | _      | 2.5                | 3.5  | mA         |

|                                                      | (_,                    | V <sub>ENABLE</sub> = 5 V, V <sub>REF</sub> = 0.8 V, No Load           |        | 40                 | 60   | mA         |

| Control Logic                                        |                        |                                                                        |        |                    |      |            |

| Logic Supply Range                                   | V <sub>cc</sub>        |                                                                        | 4.5    | 5.0                | 5.5  | V          |

| Logic Input Current                                  | I <sub>IN(1)</sub>     | All Inputs = 2.4 V                                                     | _      | <-1.0              | -10  | μА         |

|                                                      | I <sub>IN(0)</sub>     | All Inputs = 0.8 V                                                     | _      | -50                | -200 | μА         |

| Logic Input Voltage                                  | V <sub>IN(1)</sub>     | All Inputs                                                             | 2.4    | _                  |      | V          |

|                                                      | V <sub>IN(0)</sub>     | All Inputs                                                             | _      | _                  | 0.8  | V          |

| V <sub>REF</sub> Open-Circuit Voltage                | V <sub>REF(OPEN)</sub> | I <sub>REF</sub> = 0                                                   | _      | V <sub>cc</sub> /2 | _    | V          |

| Current Limit Threshold                              |                        | V <sub>REF</sub> /V <sub>SENSE</sub> at Trip Point                     | 9.5    | 10                 | 10.5 |            |

| Turn-On Delay                                        | t <sub>on</sub>        | All Drivers                                                            | _      | 1.0                | _    | μs         |

| Turn-Off Delay                                       | t <sub>off</sub>       | All Drivers                                                            |        | 1.0                | _    | μs         |

| Thermal Shutdown Temp.                               | T <sub>J</sub>         |                                                                        | _      | 165                |      | °C         |

| Logic Supply Current                                 | I <sub>cc</sub>        | V <sub>ENABLE</sub> = V <sub>REF</sub> = 2.4 V                         | _      | 15                 | 20   | mA         |

|                                                      |                        | V <sub>ENABLE</sub> = 0.8 V, V <sub>REF</sub> = 2.4 V                  | _      | 22                 | 30   | mA         |

NOTE: Tests performed at OUT  $_{\rm B}$  with V  $_{\rm PHASE}$  = 0.8 V and at OUT  $_{\rm A}$  with V  $_{\rm PHASE}$  = 2.4 V

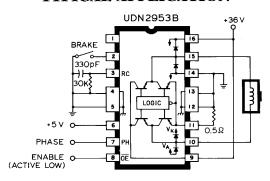

#### **APPLICATIONS INFORMATION**

The UDN2953B and UDN2954W full-bridge motion control ICs are designed for pulse-width-modulated (PWM) bidirectional interface to many types of dc (brush) servo, brushless dc, and 2-phase stepper motors. These power ICs permit various techniques of direct motor interface and offer internally and externally programmed current control. Pulse-width-modulated output current can be regulated by an (external) PWM control signal or use of an external sensing resistor (R<sub>SENSE</sub>) in combination with an RC network and/or voltage reference.

The output current trip point or sense resistor formulas are:

$$I_{TRIP}$$

=  $\frac{V_{REF}}{10 R_{SENSE}}$

$R_{SENSE}$  =  $\frac{V_{REF}}{10 I_{TRIP}}$

The allowable reference voltage range is from 2.4 V to 15 V. If unconnected, the reference input ( $V_{REF}$ ) defaults to  $V_{CC}/2$  (refer to Figure 1) and  $I_{TRIP}=0.5$  A (per typical application where  $R_S=0.5$   $\Omega$ ).

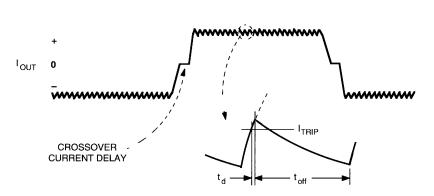

When the motor current attains the specified design value, the internal comparator triggers the monostable ('one-shot') multivibrator, which disables (switches OFF) the sink (lower) output. The actual load current may vary slightly, and the difference is (chiefly) related to the circuit propagation delays between comparator (trip point) command and power output switching. Applications involving very-low inductance windings may necessitate specific consideration; typical circuit delays ( $t_d$ ) are about 2  $\mu$ s.

After the sink ('low-side') output is switched OFF, motor current starts to decay, and the circulation path is through the ON source (upper) drive output and the flyback diode protecting the sink (lower) output. The output OFF interval is set by an external RC timing network connected to the monostable. The magnitude of the current decay is directly related to the OFF period and the duration should allow the current level to drop below the trip point before reactivating the sink output. This ON-OFF PWM cycle repeats, sustaining the desired average current to the motor winding, and continues free-running until a new input command switches the output state. The RC network values range from 20 k $\Omega$  to 100 k $\Omega$  for resistors, and capacitor values from 200 pF to 500 pF. The parallel RC network establishes the  $t_{\rm off}$  interval and directly affects the decaying motor current.

Internal timing circuitry is an alternative to the external RC timing network. However, with internal timing the logic supply current rises approximately 6 mA. Connecting the RC input to the logic supply activates internal circuitry;  $t_{off}=12~\mu s$  with  $V_{CC}=+5~V$  and  $T_A=+25~C$ , and increases with temperature.

The sink (lower) output is repeatedly re-enabled until the motor is reversed, braked, or stopped. Current control via pulse modulating the lower outputs is based on the dynamic characteristics of the much faster NPN Darlington outputs.

Another method of controlling motor current involves external circuitry to pulse modulate the OUTPUT ENABLE pin. Switching

#### TYPICAL APPLICATION

Dwg. No. A-12,649B

NOTE: Pin 3 must be connected to an RC network as shown, or to V<sub>CC</sub>. It must **NOT** be left unconnected.

(toggling) the OUTPUT ENABLE affects both the sink (low-side) and upper (high-side) outputs. Both lower and upper transient-protection diodes conduct during the OFF interval. This method of operation produces very rapid current decay. The sink driver parallel diodes (common anode pin) are connected to ground; the source output flyback diodes (common cathode pin) are connected to the motor supply (VBB). The RC input pin is to be terminated to ground through 20 k $\Omega$  (minimum).

The motor is braked by simultaneously activating both source driver outputs and disabling both sink outputs. Basically, this shorts both terminals of the motor winding to the supply. The back EMF (electromotive force) of the motor develops current which functions as a dynamic brake. Typically, the braking current approaches the values related to a locked rotor (or stall) condition. Fundamentally, locked rotor (or stall) current is dependent upon the motor winding impedance and driver output ON characteristics. Internal current control circuitry is not operational during braking. Therefore, designers should exercise caution to ensure that the current produced by the back EMF does not exceed the absolute maximum ratings of the power outputs.

Figure 1

VCC

SOK

VREF/BRAKE

LOGIC

R SENSE

Dwg. No. A-13,025

Figure 2

Dwg. WM-003-1

In bidirectional drive applications, especially dc (brush) servos, the PHASE input is utilized for direction control. The current generated by back EMF at reversal is comparable to that of dynamic braking, and should be limited to the absolute maximum output current rating.

An internally generated deadtime (approximately 3  $\mu$ s) precludes the high crossover (or 'shoot-through') currents associated with momentary, overlapping conduction of both upper and lower outputs. This very abrupt, coincident-ON mode occurs with change of direction (PHASE reversal) and/or dynamic braking.

Integrated thermal shutdown protection circuitry switches OFF all power outputs should the junction temperature exceed +165°C (typical). The thermal protection is designed to avoid power IC failures stemming from extreme, excessive junction heating. Thermal shutdown self protection does not afford a proper safeguard from shorted load and/or shorted output conditions, and should not be operated as such. The thermal self-protection circuitry has a (typical) hysteresis of 8°C.

The printed wiring board should utilize a large, heavy ground plane. To optimize power IC performance, the package should be soldered directly into the circuit board. The ground side of  $R_S$  should have an individual path to the ground terminal(s) of the device. Also, the load supply ( $V_{BB}$ ) should be closely decoupled with an electrolytic capacitor of between 10  $\mu F$  and 100  $\mu F$  (typically  $\geq$ 47  $\mu F$ ) depending on printed wiring board layout.

#### **CURRENT CONTROL OPTIONS**

|                          | Circuit Terminal                  |                      |                      |               |  |

|--------------------------|-----------------------------------|----------------------|----------------------|---------------|--|

| Control Option           | V <sub>REF</sub> /BRAKE           | RC (TIMING)          | V <sub>SENSE</sub>   | OUTPUT ENABLE |  |

| No PWM                   | V <sub>CC</sub> or High           | ≥20 kΩ to Ground     | Ground               | Low           |  |

| PWM with Internal Timing | V <sub>CC</sub> or High           | V <sub>CC</sub>      | R <sub>SENSE</sub>   | Low           |  |

| PWM with External Timing | 2.4 V or 15 V* or V <sub>CC</sub> | 20-100 kΩ/200-500 pF | R <sub>SENSE</sub>   | Low           |  |

| External PWM             | V <sub>CC</sub> or High           | ≥20 kΩ to Ground     | R <sub>SENSE</sub> † | Toggle†       |  |

<sup>\*</sup> Programmed reference, i.e., A/D converter.

$V_{PHASE}$

<sup>†</sup> Primarily, closed-loop speed and/or current control applications. ITRIP can be peak (or default) limit for protecting motor and/or driver IC.

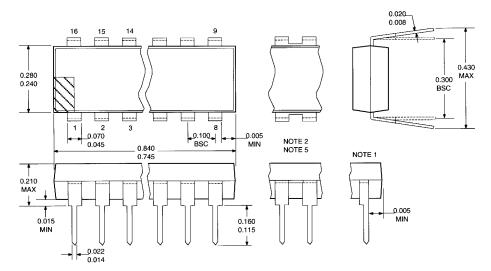

#### **UDN2953B**

#### **Dimensions in Inches**

Dwg. MA-001-17 in

# Dimensions in Millimeters (Based on 1" = 25.4 mm)

Dwg. MA-001-17 mm

NOTES: 1. Leads 1, 8, 9, and 16 may be half leads at vendor's option.

- 2. Webbed lead frame. Leads indicated are internally one piece.

- 3. Lead thickness is measured at seating plane or below.

- 4. Lead spacing tolerance is non-cumulative.

- 5. Exact body and lead configuration at vendor's option within limits shown.

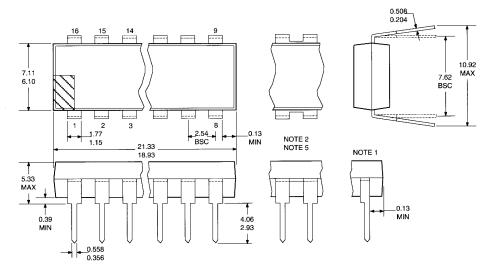

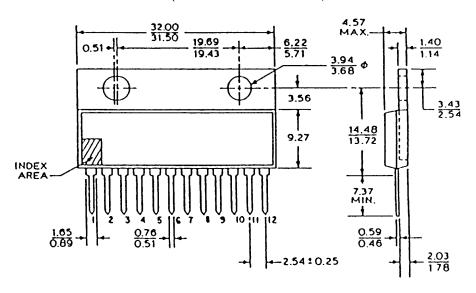

#### **UDN2954W**

#### **Dimensions in Inches**

Dwg. No. A-13,652 in

# Dimensions in Millimeters (Based on 1" = 25.4 mm)

Dwg. No. A-13,652 mm

NOTES: 1. Lead thickness is measured at seating plane or below.

- 2. Lead spacing tolerance is non-cumulative.

- 3. Exact body and lead configuration at vendor's option within limits shown.

- 4. Lead gauge plane is 0.030" (0.762 mm) below seating plane.