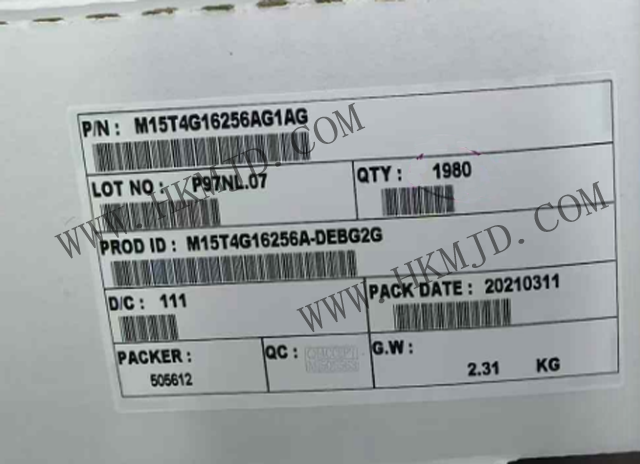

明佳达电子有限公司【供应】存储芯片 ESMT M15T4G16256A-DEBG2G DDR3(L) SDRAM 32M x 16 位 x 8 组,全新原装,欢迎咨询!!!

4Gb Double-Data-Rate-3 (DDR3(L)) DRAM 采用双数据速率架构,可实现高速运行。它内部配置为八组 DRAM。4Gb 芯片被组织成 32Mbit x 16 I/O x 8 组器件。这些同步器件可实现高达 1866 Mb/秒/引脚的高速双数据率传输速率,适用于一般应用。

特点

接口和电源

˗ SSTL_135: VDD/VDDQ = 1.35V(-0.067V/+0.1V)

˗ SSTL_15: VDD/VDDQ = 1.5V(±0.075V)

符合 JEDEC DDR3(L) 标准

˗ 8n 预取架构

˗ 差分时钟 (CK/CK) 和数据选通 (DQS/DQS)

˗ DQ、DQS 和 DM 的双倍数据速率

数据完整性

˗ 自动刷新和自刷新模式

省电模式

˗ 部分阵列自刷新(PASR)

˗掉电模式

信号完整性

˗ 可配置 DS 以实现系统兼容性

˗ 可配置的片上终端

˗ 通过外部 ZQ 焊盘实现 DS/ODT 阻抗精度的 ZQ 校准(240 欧姆 ± 1)

信号同步

˗ 通过 MR 设置进行写均衡

˗ 通过 MPR 读取电平

可编程功能

˗ CAS 延迟(5/6/7/8/9/10/11/12/13/14/15/16)

˗ CAS 写入延迟(5/6/7/8/9/10/11/12)

˗ 加法延迟(0/CL-1/CL-2)

˗写恢复时间(5/6/7/8/10/12/14/16)

˗ 突发类型(连续/交错)

˗ 突发长度(BL8/BC4/BC4 或实时 8)

˗ 自刷新温度范围(正常/扩展)

˗ 输出驱动器阻抗(34/40)

˗ RTT_Nom 的片上终端(20/30/40/60/120)

˗ RTT_WR(60/120)的裸片端接

˗ 预充电降频(慢/快)

如有兴趣,请联系陈先生:

QQ:1668527835

电话:13410018555

邮箱:chen13410018555@163.com

网站网址:www.szmjd.com